Un nuovo chip ad alta prestazione è stato progettato per poter sostenere i grandi carichi di lavoro e quei calcoli che sarebbero difficili da fare in poco tempo.

L’EPI, acronimo di European Processor Initiative, ha dato vita ad un chip in grado di poter realizzare calcoli molto rapidamente e in modo indipendente, sintetizzato in HPC con precisione, per l’Unione Europea, basandosi principalmente sugli acceleratori personalizzati di RISC-V.

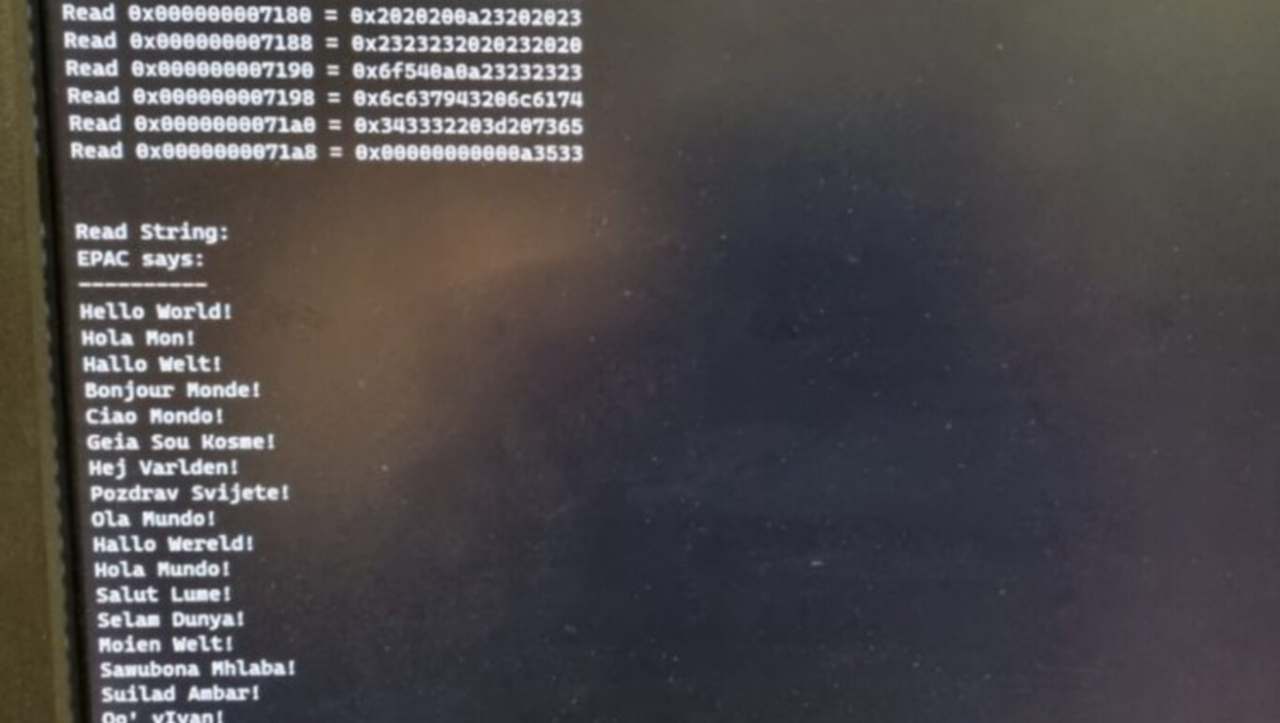

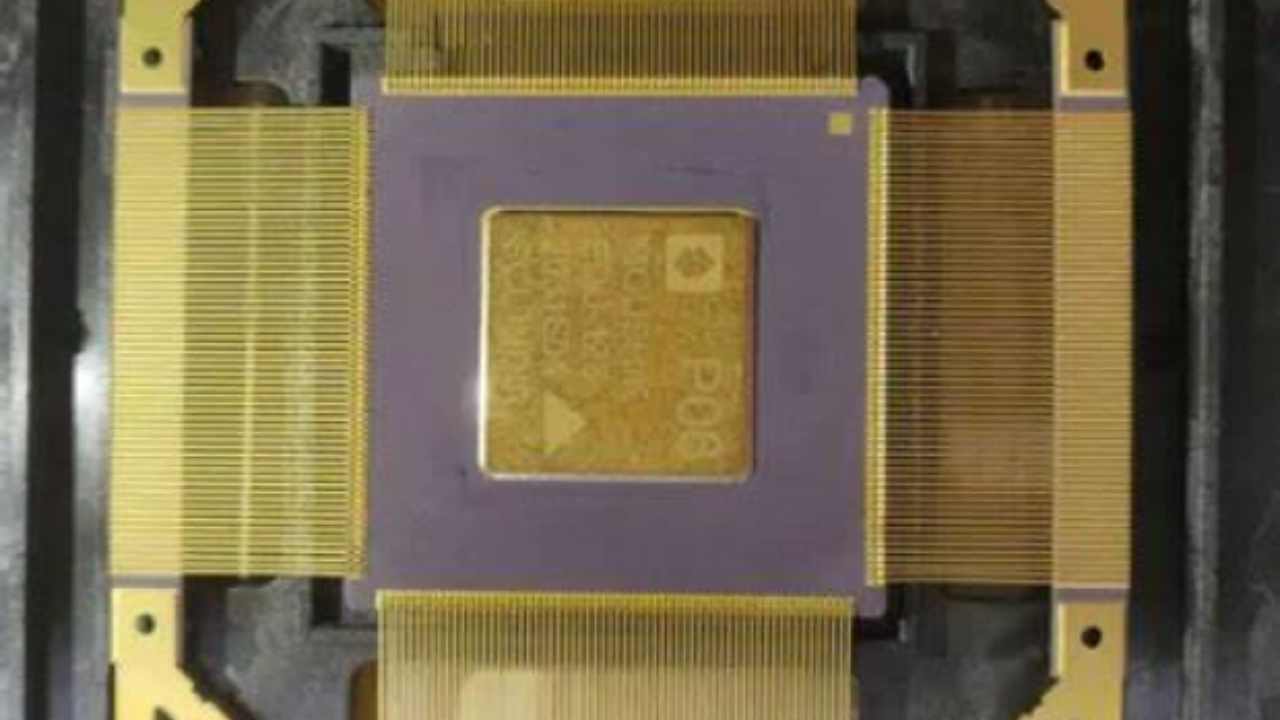

Questi chip EPAC, che prendono il nome di European Processor Accelerator, possono effettuare una grande quantità di calcoli ad alte prestazioni e rendimento. Tuttavia, non essendo ancora stato ufficializzato, è in fase di testing presso i laboratori di EPI, di conseguenza è un prototipo.

Il progetto

L’ideazione del chip ha richiesto il supporto di 28 partner di 10 paesi europei, e che saranno in grado di fornire una tecnologia talmente avanzata e innovativa da rendere l’EPI uno strumento indispensabile.

Mirano a costruire un sistema HPC che possa lavorare da solo, ma anche di essere personalizzato. Ne parlano al riguardo dicendo che: “Un segmento chiave delle attività EPI è lo sviluppo e la dimostrazione di IP di processori interamente sviluppati in Europa basati sulla Instruction Set Architecture RISC-V, fornendo core acceleratori efficienti dal punto di vista energetico e ad alto rendimento denominati EPAC.”

LEGGI ANCHE: Azienda Pro Trump nel mirino di Anonymous: ecco cosa sta succedendo

Ed infatti le promesse sono state mantenute a pieno dal momento che, i primi chip, hanno avuto modo di essere messi alla prova direttamente nei laboratori di EPI, come già accennato ad inizio articolo.

Caratteristiche tecniche

I processori RISC-V sono stati creati per acceleratori multi-purpose, incentrati sull’ISA RISC-V e sulla sua guida di design. La CPU ha quattro tile di Vector Processing Unit, costituite da core Avispado RISC-V, progettato da SemiDynamics e da altri elementi di elaborazione vettoriale creati dal Barcelona Supercomputing Center e dall’Università di Zagabria. Inoltre, in ogni tile, vi sono dei nodi homi e cache L2, nonché i contributi di Chalmers e FORTH.

Sono stati aggiunti anche gli acceleratori Stencil e Tensor (STX) progettati da Fraunhofer IIS, ITWM ed ETH Zürich, mentre il processore a precisione variabile, chiamato VRP, è stato creato da CEA LIST. Il collegamento di questi componenti è dovuto ad un router Network-on-Chip, denominato NoC, veloce e SERDES sviluppato da EXTOLL. Infine, è possibile che ci saranno delle opzioni I/O DDR5 e PCle Gen4 o 5 da utilizzare.

LEGGI ANCHE: Truffa dei pacchi trattenuti: ecco la versione di DHL e perché non dovreste mai aprire l’SMS

Il chip è stato realizzato su un nodo semiconduttore a bassa potenza FDX a 22nm di GlobalFoundries, il quale è riuscito ad effettuare il package dell’EPI in un’area di 26,97 mm² per il die. Il test è di tipo FCHGA con 22×22 sfere di saldatura in un array a griglia, mentre il chip ha una frequenza di almeno 1GHz.